## **EDN** europe

### Keysight & Our Distributor Network Bidd Hastrument RIGHT Experise. Basic Instruments

February–April 2015

KEYSIGHT

#### Touchscreen interface makes versatile oscilloscope measurements easier than ever before. SEE PAGE 3

FEBRUARY 2015

## FEBRUARY 2015

www.edn-europe.com

### **Raspberry Pi - The Sequel**

The World's Largest Selection of Electronic Components Available for Immediate Shipment!<sup>®</sup>

# FLOBAL COVERAGE

## Join us at embedded world 2015

Nuremberg, Germany 24 - 26 February 2015 Hall 4A Booth 631

1,000,000+ PRODUCTS IN STOCK

> **3.9 MILLION PARTS ONLINE**

650+ INDUSTRY-LEADING SUPPLIERS

> 100% AUTHORIZED DISTRIBUTOR

#### FIND CONTACT AND ORDERING INFORMATION FOR YOUR REGION AT DIGIKEY.COM/EUROPE

\*A shipping charge of €18.00 (£12.00) will be billed on all orders of less than €65.00 (£50.00). All orders are shipped via UPS for delivery within 1-3 days (dependent on final destination). No handling fees. All prices are in euro and British pound sterling. If excessive weight or unique circumstances require deviation from this charge, customers will be contacted prior to shipping order. Digl-Key is an authorized distributor for all supplier partners. New product added daily. © 2015 Digl-Key Corporation, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

## COVER

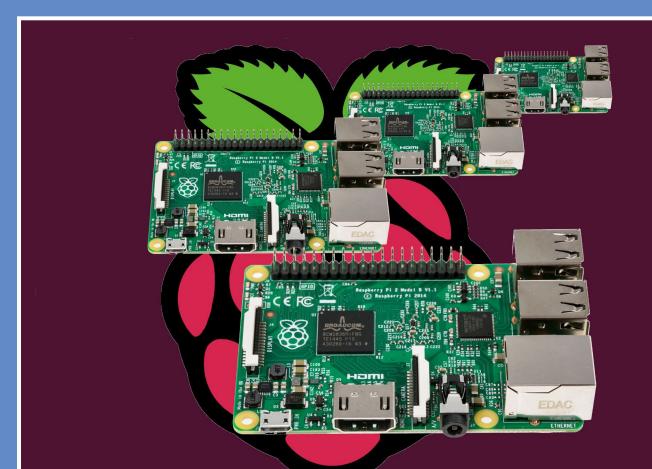

#### Raspberry Pi 2 steps up to 4-core CPU, doubles memory, still for \$35

By some margin the most popular item in our pages this month has been the introduction of the second-generation Raspberry Pi computer board. It is now three years since the debut of the first Raspberry Pi, in which time it has sold over 4.5 million units, in a number of guises. In terms of sales volume, say its makers, it has "continued to surprise". When first put into production they thought it might sell 10 or 20,000 units in its first year; a spokesman for one of its distributors RS Components recalled that they first listed it with some caution, only to have the volume of orders stress RS' website.

Much was made initially of its role in education, where it has become something of cult item. In those three years, its applications have spread far beyond that space: as well as pervading the "maker" domain, it has now become a widely-used computing unit in many embedded control and supervisory functions. Read more on page 6, and from the two linked items there.

### **FEATUREARTICLES**

- 17 GPU Compute and OpenCL: an introduction – Part 2 by Freescale Semiconductor

- 19 Bring security into development and verification by Mike Bartley & Declan O'Riordan, TVS

- 21 High dynamic range IF receiver, microwave modem design by Paul Hendriks, Analog Devices

- 23 Choosing the right wireless mesh network protocol for the Industrial Internet of Things by Ross Yu, Dust Networks Division of Linear Technology

- 24 Beam-forming antennas: essential to the next phase of mobile network growth by Victor Fernandez, Anritsu

#### **ONLINE THIS MONTH;**

Modern design tools facilitate tuning DDR4 signal paths By Ben Jordan, Altium

Integrating safety and security into connected medical devices by Lauri Ora, ARM

### **EDN's columns**

#### 4 EDN.comment

How "off" is "off" or; will the IoT save or soak up power?

7 Pulse

Raspberry Pi 2; AC power analyser; Sub-threshold ARM core; MEMS RF switches

- 27 Designing Robust, Fully Isolated (Data & Power) I2C/PMBus Data Interfaces by Maurice O'Brien, Analog Devices

- **39 Tales from the Cube** Fixing a mainframe with a lunch bag by Orin Laney

#### **35** Product Roundup

Nano-power DC/DCs; Brighter white LEDs; Battery pack balancers; Low-Rds(on) switches; SiC MOSFETs

- 28 Design Ideas

- 29 Circuit gates pulse train without truncating

- 31 Circuit lets AGC amp hold its gain

- 33 Linear ramp generator uses one op-amp

recently spoke with Senior VP of power supply maker CUI, Mark Adams, on the subject of new mandates for energy efficiency that will be required of external "adaptor"-style equipment power supplies. CUI thinks that the market – that's you – isn't sufficiently aware of some fairly imminent changes that affect, in this instance, equipment sold into the US market. Imminent, that is, in terms of getting a supply chain organised and stocked, and any necessary design changes made, by the key date, which is February 2016.

We'll come back to this topic but, briefly, the parameters of this shift are; it applies to equipment for sale in the US; it relates only to adaptor supplies; and it focusses on standby power levels. The change is to the "Level VI" (these things are denoted in Roman numerals) specification and in the case of the US marks a significant shift because the legislation there is stepping directly from Level IV to Level VI. The change also brings into scope more powerful (to 250W) external supplies than prior regulations encompassed. There's an algorithm, but broadly, think in terms of 500 mW standby having to drop to 100 mW. Naturally, CUI would like you to know that they saw this coming and can sell you compliant hardware very soon.

So far, so green; there is of course the usual calculation that takes standby power levels of such devices, multiplies them up assuming they are all left connected when inactive, and renders the results in the metric of numbers-of-power-stations of wasted supply. And, by extension, the reduction

## HOW "OFF" IS "OFF"?

in that figure of waste, that the legislation can claim to have achieved – or will achieve. I have never been entirely convinced of the validity of those calculations, although the basic principle is sound. They are somewhat latitude-dependent; standby dissipation is especially wasteful when it happens in an air-conditioned environment but here at 52degrees north, I have to heat my home for about 7 months of the year and my devices in standby are mostly just contributing a (small) part of the base-load of doing so. Not, therefore, legitimately to be entered in the "waste" column. But even if you don't entirely accept the wasted energy totals, more efficient supplies should appeal simply on grounds of engineering elegance, if nothing else.

The conversation with Mark Adams reminded me of a slightly different - but related - question he raised recently in a blog entry; Will the Internet of Things deliver power savings or will it be a massive power drain? On one side of this equation, many of the problems that the IoT aspires to solve are related to doing things more efficiently. There is the whole smart-grid domain, to take just one example: although much of that is concerned with limiting peak load rather the trimming absolute power levels. Monitoring the environment, shutting down what's not needed at any given instant: all very worthy. But will there be an overall saving when you take into account the countervailing factor: there is going to be a lot of connected devices. Not all of them can be energy-harvesting, power-sipping motes or nodes, with minuscule duty cycles; big numbers are going to be network-connected, always-on and line-powered. Not to mention the build-up of infrastructure ("cloud", if you like) resources to service all the projected datacentric gadgets.

Mark Adams' commentary linked to, and reminded me of, a report issued in 2014 by the International Energy Agency (IEA), entitled Network Standby. Its authors point to the proliferation of networkconnected devices that (they say) maintain full network connectivity (or nearly so) when their top-level functionality is not being used and when they are notionally "in standby". Set-top boxes, games consoles, broadband modems and (as the IoT phenomenon develops) assorted gateways being cases in point. Some of those, the IEA report suggests, may run at as much as 80% of "on" levels when nominally in "standby". The report makes a plea for more sophisticated designs; "Implementing best available technologies could reduce the energy demand of network-enabled devices by up to 65%. In the absence of strong market drivers to optimise the energy performance of these devices, policy intervention is needed." More legislation, in other words.

You can, as I've said here before, make your own selection of number-of-billions of connected device that await us in our near future, from the many authoritative (or otherwise) forecasts that are out there. Whether you believe that the whole thing is overstated; or that we have only imagined a fraction of it: the idea that it will be net-energy-reductive looks very unlikely.

## Welcome to the New Standard.

The next generation of oscilloscope technology.

6000 X-Series The new standard in price performance

- Industry's best price performance

- Unmatched signal visualization

- Unprecedented instrument integration

- S-Series The new standard in superior measurements

- Industry's best signal integrity

- Most advanced platform

- Broadest range of capabilities

|                                  | Keysight InfiniiVision 6000 X-Series                                                                                                                                               | Keysight Infiniium S-Series                                                                                                      |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Bandwidth                        | 1 GHz – 6 GHz                                                                                                                                                                      | 500 MHz – 8 GHz                                                                                                                  |

| Max sample rate                  | 20 GSa/s                                                                                                                                                                           | 20 GSa/s                                                                                                                         |

| Industry-leading<br>noise floor* | 115 μVrms (1 mV/div)                                                                                                                                                               | 90 μVrms (1 mV/div)                                                                                                              |

| Plus                             | <ul> <li>450,000 wfms/s update rate</li> <li>Hardware InfiniiScan Zone trigger</li> <li>12.1" capacitive multi-touch</li> <li>6 instruments in 1</li> <li>Voice control</li> </ul> | <ul> <li>10-bit ADC</li> <li>100 Mpts std. memory</li> <li>15" capacitive multi-touch</li> <li>Advanced Infiniium GUI</li> </ul> |

KEYSIGHT TECHNOLOGIES

Unlocking Measurement Insights

Experience the difference for yourself. See a live demo today! www.keysight.com/find/anewstandard

© Keysight Technologies, Inc. 2015 \* at 1 GHz

# DUSE

## From 50 MHz to 4 GHz: Powerful oscilloscopes from the T&M expert.

Fast operation, easy to use, precise measurements – That's Rohde & Schwarz oscilloscopes.

R&S®RTO: Analyze faster. See more. (Bandwidths: 600 MHz to 4 GHz) R&S®RTE: Easy. Powerful. (Bandwidths: 200 MHz to 2 GHz) R&S®RTM: Turn on. Measure. (Bandwidths: 200 MHz to 1 GHz) R&S®HM03000: Your everyday scope. (Bandwidths: 300 MHz to 500 MHz) R&S®HM0 Compact: Great Value. (Bandwidths: 70 MHz to 200 MHz) R&S®HM0 1002: Great Value. (Bandwidths: 50 MHz to 100 MHz)

All Rohde & Schwarz oscilloscopes incorporate time domain, logic, protocol and frequency analysis in a single device.

Take the dive at www.scope-of-the-art.com/ad/all

Please visit us at the **Embedded World** in Nuremberg, hall 4, booth 218

## Raspberry Pi 2, model B; 6x processing power, 2x memory

he Raspberry Pi 2 Model B has four, faster processor cores and a doubling in memory capacity to 1 GB. The board incorporates the Broadcom BCM2836 application processor, containing an ARM Cortex-A7 guadcore CPU running at 800/900 MHz. This new processor makes the Raspberry Pi 2 more than six times more powerful than the first generation Raspberry Pi Model B+. The board lavout. multimedia subsystem and peripherals remain fully compatible with the Raspberry Pi Model B+, including the use of the extensive 40-pin GPIO (General Purpose Input Output) connector, four USB ports and an efficient switching power supply. The board now hosts 1 GB of RAM, and boots in less than half the time of its predecessor. All previous Raspberry Pi projects are compatible with the new Raspberry Pi 2 Model B, and the expanded GPIO pins, advanced power management and connectivity, make it possible to connect up to four USB devices, including some powered devices such as hard drives. The 40-pin GPIO enables multiple sensors, connectors and expansion boards to be added, with the first 26 pins identical to the Model A and B boards, for full backward compatibility. Introducing the second-generation Raspberry Pi, founder Eben Upton offers some insights into the varied applications where he sees the Pi being used, in addition to its well-publicised role in education. Upton acknowledges that the first-generation Pi, while it could be used "as a PC", was at the limits of its performance in that role. Raspberry Pi 2, he says, marks, "a transition to a new world." In addition to the less demanding task it has been applied to – such as the education aspect – the new version will readily handle being deployed "just as a PC."

Embedded users who have designed in the existing model B+ and don't wish to make any design changes will continue to have that product available. Upton adds that a compute module derived from the Raspberry Pi 2 is an anticipated project/product, but at present there is no projected date for its release. For embedded use of the compute module, Upton says that his objective is to get to the point – both from the supply side, and from users perceptions - where, "it makes no sense not to use it at any volume under 50,000 units." Upton adds that Raspberry Pi has seen varied deployment in embedded functions, often in control and supervisory roles in larger items of equipment. He sees the Pi being valued in that context because, "It is cheaper, has higher reliability, and [crucially] better stability," than a customdesigned alternative or any other off-the-shelf option. Two years of engineering has gone into the Pi 2; a major part of this has been in cost-reduction, so that the board can be manufactured and delivered for the same price as the first-generation issue; but also into ensuring stability and reliability. Complete

Click right and also here.

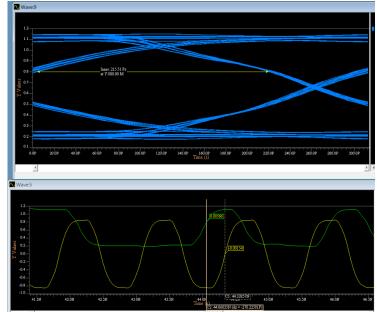

## AC power analysis and oscilloscope display, in a single instrument

Keysight Technologies has introduced a power analyser with touch-operated oscilloscope waveform display functions; engineers will no longer need two separate instruments to charac-

is intended for engineers who are designing and testing electronic power conversion systems to access dynamic views of current, voltage and power, in projects such as power inverters or con-

terise power waveforms. There will be two basic versions, for singlephase and 3-phase power analysis. Combining accurate power measurements and touch-driven oscilloscope waveform viewing capability in a single instrument, the IntegraVision power analyser verters, universal power supplies, battery systems, vehicle and aircraft power systems, lighting systems/electronic ballasts and appliances.

The IntegraVision power analyser has isolated inputs rated up to 1,000 Vrms (Cat II). The instru-

ments offer external sensor inputs and 2A(RMS) and 50 A(RMS) direct current inputs, standard on all channels. The external sensor input supports current probes and transducers up to 10V full scale. Eliminating a separate oscilloscope in the measurement setup decreases test complexity and reduces configuration time, Keysight says; its IntegraVision power analysers are designed to quickly and interactively measure AC and DC power consumption, power conversion efficiency, operational response to stimulus, and common AC power parameters such as frequency, phase and harmonics - all with 0.05% basic accuracy and 16-bit resolution. The power analyser enables engineers to characterise power consumption under highly dynamic conditions with 5 Msamples/sec digitising rate and 2 MHz bandwidth.

### 12-way RF MEMS ohmic switch targets LTE-A handsets

SP12T switch made using DelfMEMS' FreeFlex MEMS technology will, the company says, deliver the performance needed for next generation smartphone handsets. The developer of RF MEMS switching solutions will demonstrate what it believes to be the first twelve throw, RF MEMS ohmic contact switch at Mobile World Congress (MWC) 2015. Cybele Rolland, DelfMEMS CEO, explains, "Until now, companies have tended towards the capacitive switch solution route. We chose the harder route of contact or Ohmic switching because of the superior performance and have succeeded in creating the world's first, fully functional version..." The potential benefits of **DelfMEMS RF-MEMS switching** solution are being able to deliver the performance required for the next generation of handsets, LTE-A and beyond, with ultra-low in-

sertion loss, outstanding isolation and superior linearity to enable full uplink carrier aggregation. The early samples of the SP12T switch, which will be shown at MWC, have performance levels that are comparable to the current

market leading solutions but for production devices the company expects performance levels will be significantly higher, enabling the full potential of LTE-A, and beyond, data rates for both up-

load and download to finally be achieved.

## Blue-light optical encoder ICs boost resolution and performance

C-Haus has developed sensor chips for optical position encoders with photodiodes optimised for blue wavelengths. The shorter wavelength and penetration of

blue-light photons can improve the resolution, signal amplitude, harmonic distortion. and jitter performance of incremental and absolute encoders, the company says. Blue light causes less diffraction at the same slot width compared to higher wavelengths. thus resulting in sharper imaging. Modern semiconductor processes provide small, shallow structures which can take advan-

tage of the shorter penetration of blue light to improve efficiency. Smaller structures allow an interlaced photodiode layout which produces sine and cosine encoder signals with lower offset. In addition, a high fillfactor for the photosensitive areas is achieved by an equivalent geometrical transformation.

Long term temperature-stable blue LEDs are available, iC-Haus continues, which outperform the IR and red LEDs used in encoders so far, because they offer higher light yield and efficiency at lower cost. Optical position sensors benefit as a result of the technological progress of both LED and CMOS technology. iC-Haus has optimised its

incremental scanners in its high resolution iCPT H Series for blue light, undet the platform name Encoder blue. The encoder chips combine optimised scanning and signal interpolation in the smallest available space: a flat 5 x 5 mm optoQFN package with a plane window. Due to the phased-array structure of the optochips, a minimal scanning area of only 1.9 x 3.1 mm is sufficient to

generate 10,000 pulses per revolution using a code disc of 26mm diameter.

## Snapshot hyperspectral image sensors use mosaic filters

Belgian research centre imec has disclosed a new set of snapshot hyperspectral CMOS image sensors featuring spectral filter structures in a mosaic layout, processed per-pixel on 4x4 and 5x5 'Bayer-like' arrays. These hyperspectral filter structures are

imec

processed at waferlevel on commercially available CMOS image sensor wafers, enabling extremely compact, low cost and mass-producible hyperspectral (multiwavelength, beyond the visible) imaging solu-

tions. This paves the way, imec says, to applications ranging from machine vision, medical imaging, precision agriculture to higher volume industries such as security, automotive and consumer electronic devices.

Andy Lambrechts, program manager at imec, comments, "The new mosaic architecture, and extended spectral range, brings unique advantages compared to our previously announced hyperspectral linescan sensors for applications in which scanning would not be practical. It enables spectral imaging in a truly compact, tiny form-factor, that can even be scaled to handheld devices. From

the technology standpoint, we have now successfully demonstrated linescan and tiled sensors, in which spectral filters cover many pixels, to mosaic sensors, in which filters vary from pixel to pixel. At the same time,

the spectral range is extended and now covers down to 470 nm." The newly developed mosaic sensors feature one spectral filter per pixel, arranged in mosaics of 4x4 (16 spectral bands) or 5x5 (25 spectral bands) deposited onto a full array of 2 Million pixels 5.5

µm size CMOSIS CMV2000 sensor.

## ARM MCU built in sub-threshold technology for 10-fold power reduction

Micro says its Apollo microcontrollers redefine 'low power' with up to 10x reduction in energy consumption: the ARM Cortex-M4F microcontrollers are based on subthreshold voltage technology.

Ambig Micro, based in Austin, Texas, says it has resolved the issues surrounding placing logic built with sub-threshold technology into volume production in a standard CMOS process. Its first announced products are the Apollo family of four 32-bit ARM Cortex-M4F microcontrollers (MCUs). In real-world applications, their energy consumption is typically 5 to 10 times lower than that of MCUs of comparable performance, resulting in far longer battery life in wearable electronics and other battery-powered applications. The reduction in energy consumption is achieved using Ambig's patented Subthreshold Power Optimized Technology (SPOT) platform. In sub-threshold logic, individual

transistors are never turned completely on; effectively, logic levels are propagated as leakage-current or leakage-current-plus-a-bit. Dissipation is greatly reduced but the generation and detection of logic levels, and execution of logic functions, has to be stable in the face of process variations, noise, temperature drift and a range of other variables. Previous successful attempts to use sub-threshold logic (watch ICs, for example) have most often been built in in-house. dedicated fabs where process variables have been constantly tuned and refined. Ambig's claim is that it has designed structures that can maintain correct operation when implemented in a stock foundry CMOS process. "We do have to do work at the RTL level," says a company spokesman, "But the IP of the ARM MCU is untouched – this is a standard ARM core, with the floating point unit." All of the ben-

efits to power flow from the sub-

threshold implementation. Apollo MCUs optimise both active and sleep mode power (the two factors are mutually contradictory in a conventional process, the company explains). They consume 30 µA/MHz when executing instructions from flash and feature average sleep mode currents as low as 100 nA. Apollo MCUs operate at up to 24 MHz. They are available with up to 512 kB of flash and 64 kB of RAM to accommodate radio and sensor overhead in addition to application code. Communication with sensors, radios, other peripherals and an optional host processor is implemented via I<sup>2</sup>C/ SPI ports and a UART. On-chip resources include a 10 bit, 13-channel, 1 Msample/sec ADC and a temperature sensor with ±2°C accuracy. Two compact packaging options are available - a 64-pin, 4.5 x 4.5 mm BGA package with 50 GPIO and a further size-optimised 2.4 x 2.77mm, 42-pin CSP with 27 GPIO.

### "Virtual-lab" environment provides exemplars of advanced PCB design flows

entor Graphics has secured the participation of a number of industry players who make

leading-edge – especially, highspeed signalling – devices, to demonstrate the capabilities of its HyperLynx design environment for advanced and high-speed PCBs. The HyperLynx Alliance has been formed by Mentor Graphics and industry partners to provides free access to virtual reference designs plus tools, design data and identified best-practice methodologies

> for difficult SerDes and DDR design and verification challenges: companies involved from the outset are Altera. PMC-Sierra, Samtec, Inc. and eASIC. Noting that new high-speed protocols are increasingly difficult to design and verify at multi-gigabit speeds, the Alliance cloud platform provides access to taraeted vendor ref-

erence designs, tools and models, allowing engineers to evaluate and tradeoff device parameters using recommended verification methodologies and sample channel designs. Virtual labs [modules or sessions] include the complete HyperLynx design environment, partner IBIS-AMI electrical models, a reference design for test cases, and a step-by-step instruction guide. Each HyperLynx virtual lab can be completed in a few hours and is available as a future resource for users during real design and implementation stages. The alliance uses the HyperLynx tool suite for high-speed design and verification, deployed on cloud-based virtual labs to accelerate time to productivity. The virtual lab series uses partner models and reference designs with the tool suite to demonstrate ideal design methodologies to address difficult high-speed printed circuit board (PCB) SerDes and DDR design challenges. The virtual labs reduce engineering time and costs associated with evaluation design tool requests and design case setup which could take days or weeks. The labs walk through a recommended design process, helping engineers formulate their own methodologies and enabling them to evaluate trade-offs to

improve overall system performance.

## Infineon, Hella make radar sensor more affordable

#### by Christoph Hammerschmidt

nfineon and German tier one automotive equipment maker Hella KG now have jointly developed RF components for radar sensors that enable manufacturers to lower prices and power con-

sumption. Hella already produces a 24-GHz radar sensor system for blind spots. This continuously updated radar scan detects moving objects even in poor weather and independent of the direction and speed of their motion. Optimised antenna concepts facilitate an even higher measuring accuracy. Infineon's Microwave Monolithic Integrated Circuit (MMIC) using the BGT24Axx chip family, helps to increase the detection efficiency of the driver assistance system.

> It improves the signal-tonoise ratio (SNR), ensuring higher precision in the detection of objects in the blind spot. The MMICs integrate all RF components such as oscillators, amplifiers and reception branches with low-noise amplifiers and I/Q mixers on a single chip. Hella's radar system can be smaller,

more affordable and it consumes less power. The 24GHz chip family enables a custom-fit configuration of the hardware, depending on the system environment and application field.

Complete article, here

## New magnetic materials seek memory, wireless applications

class of structures called hybrid multiferroics may yield improved data storage and new wireless applications. To exploit and control magnetism, technology often relies on electromagnets, which limit hardware configurations due to their size and energy consumption. As an alternative, researchers are beginning to develop hybrid nanomaterials that are responsive to both electric and magnetic fields. These materials can save energy and space, and may open up new applications. Power savings are one incentive, but another factor is the multi-functionality they could offer, possibly leading to new forms of information storage. "Some materials exhibit spontaneous electric or magnetic order. These materials are called ferroelectric and ferromagnetic, respectively," explains Professor Sebastiaan van Dijken, leader of the Nanomagnetism and Spintronics Group at Aalto University, Espoo, Finland. "However, among

these two ferroic materials there is little overlap." Prof. Van Dijken's group received a €1.5million European Union grant in 2012, to fund a five-year project. To further its investigations, the group has developed a microscopy technique that employs an ultra-fast camera, to enable the imaging of ferroelectric-ferromagnetic coupling effects in an applied electric field with nanosecond-precision. Study objectives include finding out if, and how, it is possible to manipulate the magnetic properties of materials by electrical means in nanoscale structures and in the time frame of nanoseconds. Professor van Dijken's team have been creating hybrid structures using one stable ferroelectric material and one stable ferromagnetic material. Built at the nanoscale, thin films of each material are linked together by strong coupling at their interfac-

es, enabling them to be used as a single entity.

## Valydate schematic design analysis and verification now on Altium

Itium and Valydate, writers of software for schematic, signal and power integrity analysis, have entered a partnership aimed at easing the timeconsuming visual inspection and debugging process of electronic schematics. by integrating the design analysis and verification tool ValydateVERA into Altium Designer. The two companies say that the technology will aid in streamlining the design process and save designers hours in visually inspecting of schematics for errors.

The rising complexity of modern electronics design has ushered in a multiplying set of rules and verifications that must be manually checked for schematic design errors, regardless of which design software is used. Requiring manual validation has a dramatic impact on schedules. ValydateVERA claims to effectively streamline this process. With VERA's integration in Altium Designer, designers can now automatically inspect their schematics against a predefined checklist that takes advantage of an intelligent component library that automatically checks for thousands of error violations in schematic designs. "We've seen a steadily increasing number of customers working with complex designs who had no choice but to manually check their schematics for thousands of potential errors which adds up to countless wasted hours," said Jason Hingston, CTO at Altium.

## Thermopile array sensor identifies movement, direction and multiple objects

Panasonic Automotive & Industrial Systems has introduced what it believes to be the first surface mount thermopile array sensor. Grid-EYE features 64 thermopile elements in an 8x8 grid format that detect absolute temperatures by infrared

tures by infrared radiation. Grid-EYE is able to measure actual temperature and temperature gradients, providing thermal images. It is possible to detect multiple persons, identify positions and direction of movement, almost independent of ambient light condi-

tions without disturbing privacy as with conventional cameras.

Cost-effective and compact solutions for contactless temperature measurement across the entire specified area can configured with very accurate results. A built-in silicon lens provides a viewing angle of 60°. Measurement values can be read out via I<sup>2</sup>C interface in 1 or 10 frames per second. An interrupt signal output delivers a quick response to timecritical events or additional energy sav-

> ing capabilities in stand-by mode, offering a high degree of flexibility. Measuring 11.6 x 4.3 x 8.0mm, Grid-EYE arrays have an operating voltage of 3.3V or 5V and a typical current consumption of 4.5 mA (normal mode); 0.8 mA (stand-by mode); and 0.2 mA (sleep mode). Object tempera-

ture range is 0 to 80°C for the high gain amplification version and -20 to 100°C with low gain. Overall Temperature accuracy is  $\pm 2.5$ °C with an NETD (Noise

Equivalent Temperature Difference) of  $\pm 0.5^{\circ}$ C, depending on P/N.

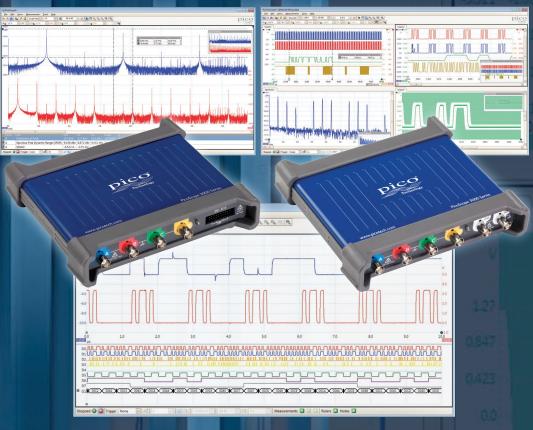

### PC-based scopes use USB 3.0, offer 512 Msample memory depth

icoScope 3000D Series oscilloscopes have up to 200 MHz bandwidth, two or four analogue channels plus 16 digital channels on the mixed-signal (MSO) models, and deep memories from 64 to 512 mega-samples. The scopes offer a maximum real-time sampling rate of 1 Gsample/ sec and feature a USB 3.0 interface; they also host a built-in arbitrary waveform generator (AWG). Deep memory enables long timebases with the fastest sampling rates; for example, at 1 Gsample/ sec sampling rate you can capture a 500 msec waveform-that's half a billion samples, Pico points outwhile hardware acceleration keeps the display updating smoothly.

The 512 Msample buffer memory can be segmented, enabling acquisition of up to 10 000 individual waveform segments of 50 000 samples, with less than 1 µsec rearm time between each segment. The oscilloscopes are multifunction, including a spectrum

analyser and arbitrary waveform generator (AWG), and advanced functions as standard, such as serial bus decoding, mask limit testing, maths channels and filtering. Advanced triggers include pulse width, interval, window, window pulse width, level dropout, window dropout, runt pulse, variable hysteresis, and logic. All triggering is

> digital, ensuring low jitter, high accuracy and single-LSB voltage resolution. MSO models combine these triggers with edge and pattern triggering on the digital inputs. Features include colour persistence display modes, automatic measurements with statistics, programmable alarms, and decoding of I<sup>2</sup>C, UART/RS232, SPI, CAN bus, LIN, FlexRay and I<sup>2</sup>S signals. Software updates include a fast persistence mode that gives updates of around

100 000 waveforms per second, while the math channels have

been expanded to include configurable filters.

#### Complete article, here

### 7½-digit DMM has 1 MHz sampling, plus graphical display

ermed by Keithley the first "graphical sampling digital multimeter" the DMM7510 combines high accuracy, integrated data visualisation, and operation via a capacitive touch screen with an interface that is modelled on the "smartphone experience". The DMM integrates a high accuracy digital multimeter, a digitiser for waveform capture, and a capacitive touchscreen user interface. Keithley says that the design philosophy of the instrument is based on helping engineers to get an in-depth understanding of their devices under test, in a context where they need to capture small signals at higher accuracy and faster speeds than traditional DMMs can provide. The Model DMM7510 uses an 18-bit conversion, with a peak sampling rate of 1 Msample/sec. Basic accuracy is 14 ppm (parts-per-million). It can display a graphical representation

of the captured samples, but Keithley is careful to point out that this is not updated as is a scope display.

You operate the instrument with a graphical touchscreen which responds to a range of provides DC accuracies "typically only found in metrologygrade instrumentation—but at about half the price of those solutions" the company asserts. The 14ppm basic 1-year accuracy applies to DC volt-

gestures (swipe, etc.) that are borrowed from smartphone and tablet computer practice (or by means of conventional rotary-knob control), and there is internal processing to carry out analysis of the captured data points.

Resolution level is selectable from  $3\frac{1}{2}$  to  $7\frac{1}{2}$  digits; the unit

age measurements. Expanded measurement ranges (100 mV, 1 $\Omega$ , and 10  $\mu$ A) enhance low level accuracy. On the 10  $\mu$ A range, resolution is therefore 1 pA: at the other end of the scale, the 7510 has a 10A

current range, without use of external shunts.

## ARM adds safety support to Cortex-R5 IP for automotive, medical and industrial markets

RM has created a comprehensive safety document set for the ARM Cortex-R5 processor to assist its adoption in safety-critical applications. The Cortex-R5 is the first in a range of ARM processors to come with a safety document set that semiconductor companies can use to demonstrate compliance with new functional safety standards. ARM notes the importance of functional safety in markets that include automotive, medical and industrial applications, and says, "The Cortex-R5 processor has a rich set of fault detection and control features and the addition of generic safety documentation means developers can now use it across the broadest range of safety applications." Part of the context, ARM notes, is that the applicable standards have evolved and recognise the role of IP, enabling ARM address the issue of functional safety directly.

The work it has done, ARM says, is at several levels; it offers support for safety-related operations and functions (dual-core lock-step operation, for example) but also provides documentation that covers not only the IP itself but the methodologies of its design. A significant proportion of the preparation for this release has, the company says, been related to process; the design process must stand up to scrutiny regarding its approach to design-for-safety and how that has been applied at all stages. This complements the fact that the company has included fault detection and control features in its IP for many years. The offering is "standards agnostic" that is re-usable across different market sectors; it supports a range of safety levels (for example, the tiered SIL structure in automotive/ industrial contexts) and is configurable, and modular. ARM has already worked with its licensees in this area, citing Texas Instruments, which offers a safety-critical-systems application and documentation package with its Hercules MCUs.

#### **GPU COMPUTE AND OPENCL: AN INTRODUCTION – PART 2**

By Nicu Penisoara, Freescale Semiconductor

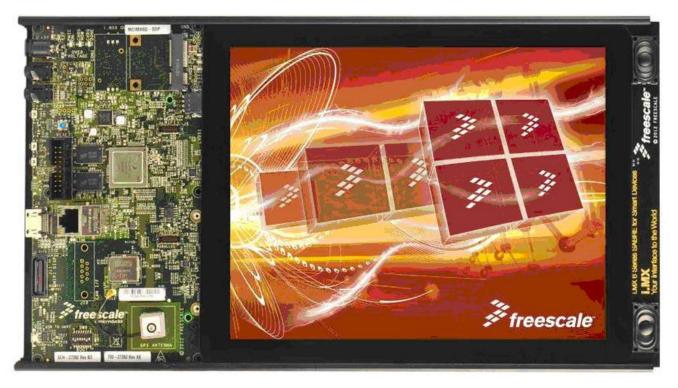

This article provides to the reader unfamiliar with the subject an introduction to the GPU evolution, current architecture, and suitability for compute intensive applications. OpenCL was introduced in this context (in the first part of the article), and in this second part a sample application is presented, together with indications on setting up the development environment, building and running the application on a Freescale i.MX6-based platform.

Editor's note; Part 1 of this article is here; the pdf download accessed by clicking the link below contains Part 1 and Part 2.

#### Overall setup and OpenCL application overview

As the reader remembers from the first part of the article, any OpenCL application has two components: one that runs on the Host (for system management, as well as control code) and a second one that runs on the Compute Device(s), typically doing the "heavy lifting" in terms of data processing. While in some systems (for example, a typical PC equipped with a graphics card), these two entities are physically separate devices, in a vast array of modern Application Processors we have available an integrated GPU, capable of running OpenCL applications.

For our demo application we will use the same i.MX6 Quad SoC that we have referred to in the first part of the article to exemplify the structure of a modern GPU from an OpenCL perspective. The Host is represented by the cluster of four ARM Cortex A9 CPUs, while the Compute Device is represented by the GC2000 GPU. As a system to run our demo application we have chosen the i.MX6 Sabre SDB, one of the reference hardware platforms for this SoC – pictured in Figure 1.

While potentially a little ambitious for a "Hello World" type application, we will put the screen of the SABRE platform to use in our applica-

#### Figure 2. Demo application output on the LCD screen

tion, as we will present an application that represents the movement of a particle system under the action of predefined forces in a closed system, with the initial set of particles given by a bitmap. Figure 2 above captures the screen output at different stages in the application execution (or particle system lifetime).

Hoping that we have generated enough interest such that reader will venture into replicating and tinkering with the application, we will look in the next sections at the system setup, Host as well as Compute device applications.

#### System setup

As a development environment for the Host we will use C under Linux. In order to build and boot a Linux system on our SABRE board, we will use the latest Freescale Linux BSP release, available on www.freescale.com , in the "Software and Tools/Software development tools" section for the i.MX6 application processor - at the time of the writing, the latest Linux BSP release is L3\_10\_53\_1.1.0.

After downloading the BSP, the steps needed to build the Linux image and boot it on the target system are presented in the "Freescale Yocto Project User's Guide" document. As for the OpenCL demo application we will use frame buffer, the recommended image to build and deploy is "fsl-image-gui" – this image has all the needed libraries required by our application.

If you want to replicate this demo on other i.MX6 based system, it is important to note that the requirements for the Linux image booted on the target are to have the gpu-viv-bin-mx6q package selected, as well as frame buffer support.

Click below for the complete article download.

Download PDF of Article

Find GPU on EETsearch

#### **BRING SECURITY INTO DEVELOPMENT AND VERIFICATION**

By Mike Bartley & Declan O'Riordan, TVS

Autonomous systems require particular attention to security and trustworthiness before deployment.

Increases in processing performance and the growing pervasiveness of communications are making it possible to create a new generation of autonomous systems, including self-guided drones and automated road vehicles as well as sophisticated industrial control systems. Many of these systems will be fed data by an array of distributed sensors, giving them much better information about their environment, allowing them to make intelligent decisions.

But the number of inputs and their connectivity to other systems on the internet provides these autonomous systems with a large attack surface, offering many possible opportunities for attackers to disrupt their operation and either take control or cause them to crash. As a result, designers of these autonomous systems need not only design for safety but take security into account in the design to ensure that the system does not become unsafe if attacked.

Numerous reports of attacks, which have increasingly focused on embedded systems such as those used to control point-of-sale (POS) systems, show how limited the industry's attention to secure design has been. Many of these penetrations by hackers have been through mistakes made in system design and implementation.

According to the IEEE Centre for Secure Design, design flaws account for 50% of software security issues, and these flaws take many forms. The Massachusetts Institute of Technology Research (MITRE) has identified 700 different kinds of software security weakness. Any given system may only have a fraction of those weaknesses but as attackers will target the weakest part of the system, even a few flaws can lead to a successful penetration.

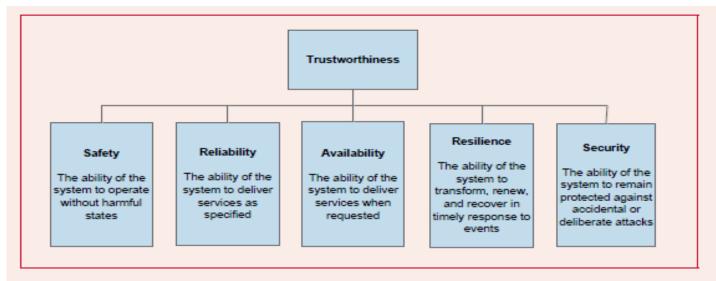

There is a need to define a development strategy that takes into account all aspects of a design that can lead to unsafe and unwanted behaviour – whether caused by intentional harm or noise in the system. The requirement is for systems that remain trustworthy in the face of external influences. To address the issue of unreliable and potentially unsafe software and systems, the Trustworthy Software Initiative

Figure 1. The PAS 754:2014 standard identifies five aspects of software trustworthiness.

backed the British Standards Institute's PAS 754:2014 standard, which identifies five aspects of software trustworthiness: safety, reliability, availability, resilience and security (Figure 1).

An important principle of building secure and trustworthy software is that security cannot be "tested in": security needs to be built in. Test is part of the overall development cycle that ensures that security and trustworthiness concerns have been addressed properly.

The BSI document describes a widely applicable approach to achieving software trustworthiness rather than mandating any specific practices or procedures. The standard calls for an appropriate set of governance and management measures to be set up before producing or using any software which has a trustworthiness requirement. PAS 754 is designed to support the building of systems that can protect themselves against both accidental and deliberate attacks.

Under the regime, design teams need to perform risk assessments that consider the

Download PDF of Article

set of assets to be protected, the nature of the adversaries that may be faced and the way in which the software may be susceptible to such challenges. From a security perspective, this includes threat assessments to determine how attacks may be made either directly or indirectly. For example, in an IoT system, an attacker will focus on the weakest nodes. These could be subverted into performing denial of service attacks on other nodes in the system, causing them to fail or to bring the whole system down even though they are not vulnerable to a direct penetration attack.

To manage risks and threats, appropriate personnel, physical, procedural and technical controls need to be deployed. Finally, PAS 754 demands a regime be set up to ensure that creators and users of software confirm that governance, risk and control decisions have been implemented.

In the continuation of this article, the authors develop the idea of a structured methodology for software development that moves consideration of security earlier in the process. Click below.

Find Security on EETsearch

### **Automotive Electronics**

## COMMUNICATIONS

#### HIGH DYNAMIC RANGE IF RECEIVER MICROWAVE MODEM DESIGN

By Paul Hendriks, Analog Devices

Microwave point to point links are an integral part of a cellular mobile network providing backhaul capability between cell sites (BTS/NodeBs) and the radio controllers (BSC/ RNCs) in over 50% of global deployments where fibre links are not cost effective to deploy.

The recent explosion in mobile network traffic driven by the market shift to smartphones (i.e streaming video) has intensified data demands and put pressure on the existing existing microwave backhaul equipment capacity. In order to scale the data throughput of the backhaul network to the needs of LTE and LTE-Advanced, the next generation microwave links will need to :

- Move to increasingly higher order digital modulation from today's QAM256 to as high as QAM4096 in the future, thus providing a 50% increase in capacity within a fixed channel assignment.

- Support channel assignments from 56 MHz today to 112 MHz in the traditional 6-42 GHz band. Every doubling of channel bandwidth provides a proportional increase in the data throughput rate capability if the Carrier-to-Noise Ration (CNR) remains constant. - Employ techniques such as polarisation diversity, channel aggregation and NxN Line-of-Sight MIMO.

As is typically the case in communication system design, this increase in throughput capability does come at a price. To support combinations of higher QAM levels and channel bandwidth, the microwave link must have more dynamic range capability to support the required minimum EVM performance performance since receiver sensitivity is reduced by 3 dB for every doubling in QAM size or bandwidth. Since the microwave equipment must remain flexible, additional consideration is required to support all possible operating scenarios while still simplifying the Rx filtering and AGC requirements for improved performance and cost reduction.

An additional industry trend is the emergence of full outdoor units (ODU) in which the full radio modem and transceiver are combined with the switching/multiplexing units and traffic interface in a self-contained box mounted on a tower or equivalent structure. This trend is driven by CAPEX/OPEX at new sites and space constraints at existing sites. Traditional "split" indoor(IDU)/outdoor(ODU) systems systems host the  $\mu$ W/RF section in the ODU with a coaxial cable connecting to the rest of the system housed in a equipment shelter (IDU). The coaxial cable can be up to 300 metres in length and carries bi-directional traffic with a diplexer being used to separate the Rx IF signal centred at 140 MHz from the Tx IF signal being centred in the 340-400 MHz range.

While this is a noteworthy trend, the majority of µW equipment shipped today and in the foreseeable future is the legacy split IDU/ ODU system. It would be beneficial to use one back-end modem transceiver architecture for design re-use purposes that supports both the legacy system and the next-generation ODU platforms. Recent advances in both high speed DAC and ADC technology operating at clock rates well above 1.5 Gsamples/ sec are now making it possible to synthesise and digitise QAM signals at high IFs with exceptional accuracy to support 4096 QAM (and beyond). Besides eliminating the need for any guadrature error correction required for traditional analogue IQ implementations, the high dynamic range along with high oversampling ratio allows the majority of the filtering to be performed in the digital domain thus reducing the amount analogue filtering and digital equalisation required to compensate for them. For the Tx signal path, high-speed DACs such as the AD9142 and AD9136 are already beginning to replace the traditional dual DAC and IQ

### COMMUNICATIONS

modulator implementations to synthesise the wideband QAM signals with exceptional EVM (error vector magnitude) performance without the need for Tx calibration. For the Rx signal path, the availability of 1.5+ Gsamples/sec ADCs well suited for these applications has lagged until the recent release of the AD6676.

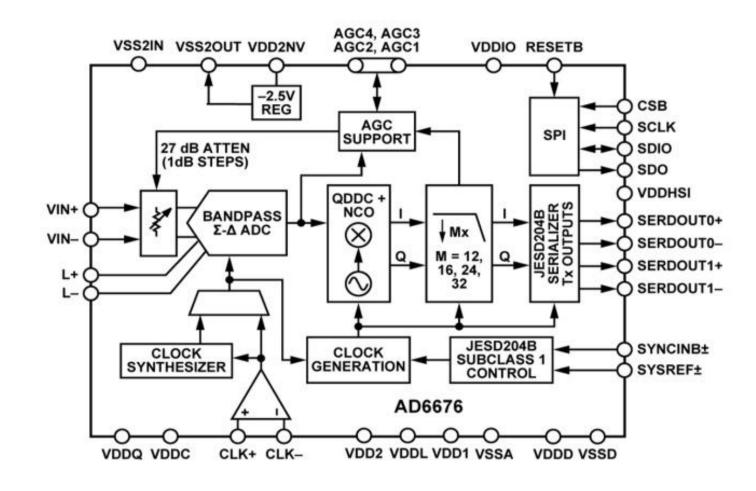

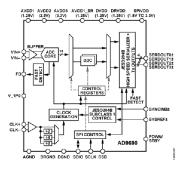

The AD6676 is the industry's first wideband IF Rx subsystem (Figure 1) based on a bandpass sigma-delta ADC supporting IF signal bandwidths up to 160 MHz while operating with an internal clock rate of up to 3.2 GHz. It is the high oversampling capability of the  $\Sigma$ - $\Delta$  ADC that greatly simplifies the IF analogue filtering requirements required in lower sampling ADCs to suppress adjacent channels (and interference/blockers) that would otherwise "alias" back onto the IF signal thus reducing the receiver's sensitivity performance. Also, it is the ADC's high dynamic range with an NSD (noise spectral density) floor of -160 dBFS/Hz (for narrowband QAM channels) that reduces the diplexer Tx-to-Rx isolation requirement or analogue AGC range that compensates for fading.

This article continues by illustrating how this new generation of ADCs can simplify traditional transceiver design, and goes on to discuss how it enables the use of higher-order QAM without adding filter complexity. Click right, for the complete article download.

Figure 1. Block diagram of the AD6676 IF Rx Subsystem

## **MESH NETWORKS**

#### **CHOOSING THE RIGHT WIRELESS MESH NETWORK PROTOCOL FOR THE INDUSTRIAL INTERNET OF THINGS**

By Ross Yu, Dust Networks

ne of the biggest promises of the Industrial Internet of Things is to make use of real-world data gathered through wireless sensor networks (WSNs) to drive higher efficiencies and to streamline business practices. The demands on WSNs are diverse, with sensors placed throughout buildings, city streets, industrial plants, tunnels and bridges, moving vehicles or in remote locations such as along pipelines and weather stations. A common requirement across such applications for the Industrial Internet of Things is for WSNs to deliver both low power and wire-like reliability and to do so across a broad spectrum of network shapes, sizes and data rates.

Wireless mesh networks have become increasingly well accepted due to their ability to cover large areas using relatively low power radios that relay messages from node to node and to maintain high reliability by using alternate pathways and channels to overcome interference. One technique in particular, called Time Synchronised Channel Hopping (TSCH) mesh networking, pioneered by Linear Technology's Dust Networks and incorporated into the WirelessHART industrial standard, is field proven to deliver the performance needed by the Industrial Internet of Things. TSCH networks typically experience better than 99.999% data reliability and all wireless nodes, even routing ones, enjoy multi-year battery life on small lithium batteries.

However, a variety of mesh networks use similar sounding networking techniques (e.g., "fre-

quency agility" vs "channel hopping," "sleepy" vs "time synchronised" meshes), and yet yield drastically different performance levels. These wireless networking details determine how such protocol level choices greatly impact a WSN's performance and the network's overall suitability for an application.

#### Wireless sensor network challenges

Since wireless is unreliable by nature, it is important to understand the sources of un-

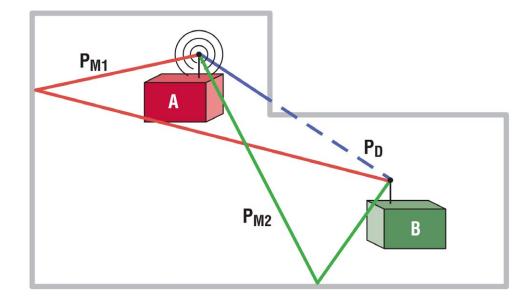

**Figure 1.** Multipath fading – A radio signal's strength at the receiver (B) is affected not only by the direct path (Pd), but also by reflections (Pm1 & Pm2) which may arrive out of phase and cause significant fading.

reliability to be able to account for them in a communications system. Unlike wired communications, where the communications signal is shielded from the outside world by cabling, RF propagates in the open air and interacts with the surrounding environment. There is the possibility for other RF transmission sources causing active interference.

However, much more common is the effect of multipath fading, where the RF message may

### Technology

## **MESH NETWORKS**

be attenuated by its own signal reflected off of surrounding surfaces and arriving out of phase (Figure 1). The effects of multipath change over time, as nearby reflective surfaces (e.g., people, cars, doors) typically move. The net result is that any one RF channel will experience significant variation in signal quality over time.

Further adding to the challenge is the fact that multipath fading is unpredictable. By definition, a network must be actively transmitting on a channel to experience (and therefore measure) the channel's performance in the face of multipath fading. Therefore, while the notion of using a simple passive signal strength measurement (RSSI) of an unused channel may be helpful to detect active interferers, it cannot predict that channel's suitability in the face of multipath fading.

Fortunately, since multipath fading affects each RF channel differently and changes over time, us-

ing channel hopping for frequency diversity minimises the negative effects of multipath fading. The challenge for WSN protocols is the ability to use channel hopping over large networks with multiple hops.

Common approaches seen in WSNs

Understanding how different WSNs perform in the face of these constraints (see the full version of this article, click below for the download) is assisted by examining techniques often used in some wireless mesh networks to address frequency diversity and to deliver low power. These can include; Single channel WSNs and channel agility; and Duty cycling by network-wide sleeping, in various forms. We can then consider the properties of Time synchronised channel hopping mesh networks, and the features and resilience that are enabled by that approach.

**Download PDF** of Article

**Find Mesh Network** on EETsearch

## THE NEW PICOSCOPE 3000 SERIES

• Up to 200 MHz analog bandwidth • Deep buffer memory up to 512 MS • MSO models with 16 digital channels • 2 or 4 analog channels • 1 GS/s real-time sampling

Includes serial bus decoding and analysis (CAN, LIN, RS232, I2C, I2S, SPI, FlexRay), segmented memory, mask testing, spectrum analysis, and software development kit (SDK) all as standard, with free software updates and five years warranty.

#### www.picotech.com/PS4048

## COMMUNICATIONS

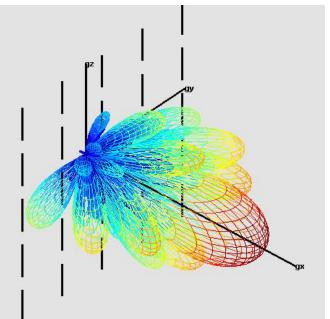

#### **BEAM-FORMING ANTENNAS: ESSENTIAL TO THE NEXT PHASE OF MOBILE NETWORK GROWTH**

#### By Victor Fernandez, Anritsu

Before 2014, LTE technology deployments worldwide were principally of the frequency division (FD-LTE) variety. It was only in 2014 that the other, time division (TD-LTE) flavour of LTE began to gain serious attention from the mobile telephone industry.

One of the main benefits of TD-LTE is its ability to support the use of beam-forming (that is, highly directional) transmitting antennas. Beamforming antennas offer network operators important benefits, enabling a more flexible and efficient use of network infrastructure and, in some circumstances, a markedly better quality of service to customers.

This means that both manufacturers and users of antennas and base transmitter station (BTS) equipment are currently exploring new approaches to the design, production, installation and use of beam-forming antennas. This article outlines methods engineers may use to design and build beam-forming antenna prototypes, and the role that specialised RF measurement instrumentation can play in the evaluation of such prototypes.

### Comparison of multi-antenna operating modes

The radio access technologies used in modern communications networks rely to a large extent on various multi-antenna systems to achieve high data rates or to improve the quality of transmission to users at the perimeter of a cell. These multi-antenna systems may be of the multiple-input, multiple-output (MIMO) type, single-input, multiple-output (SIMO) or multipleinput, single-output (MISO).

In a BTS, a multi-antenna system may be used to transmit signals by one of two opposing and clearly differentiated techniques. These techniques are commonly confused.

One use of multiple antennas is to transmit a different data stream through each antenna. This is possible when there is a low degree of correlation between the different transmission paths, for instance because the transmitter is in an environment which tends to scatter RF transmissions, causing each data stream to attempt a different path to the receiver. In this case, the receiver sees each antenna as an independent signal source, and readily distinguishes the different data streams. The effect is to increase the overall data rate. This technique is called spatial multiplexing.

The other use of a multi-antenna system is possible when all the transmission paths are closely correlated, and every signal is affected by the transmission medium in a similar way – for example in an environment subject to negligible scattering, or when the antennas are mounted close to each other. In this case, the multiple antennas can operate as though they were a single, high-power antenna with its main

## COMMUNICATIONS

lobe illuminating a specific area.

When an antenna array is used in this way, it is a beam-forming antenna. The effect is to concentrate the available bandwidth in the targeted area, improving the quality of transmission or the signal-to-interference-plus-noise ratio (SINR).

FD-LTE can employ multi-antenna systems for spatial multiplexing very effectively, since the multiple-carrier waveforms it uses, such as orthogonal frequency division multiplexing (OFDM), can be perfectly matched to this kind of transmission system architecture.

TD-LTE, on the other hand, can make particularly good use of beam-forming antennas, as the uplink and downlink are duplexed in the time domain and, more important, transmitted and received signals are at the same frequency.

Beam-forming antenna technology, then, is important to the deployment of today's TD-LTE technology, but it is also expected to play an important part in 5G network infrastructure, which will combine enhancements to LTE with new radio access technologies. This is because of the requirement to support 'network densification'– that is, the deployment of small cells with a single carrier waveform to serve small areas packed simultaneously with many subscribers. This will be achieved through the implementation of so called 'massive MIMO' beam-forming techniques.

## Techniques for realising a beam-forming antenna

A beam-forming antenna may be realised either mechanically or electronically.

The mechanical method requires the physical manipulation of the antennas to adjust their position and orientation, in order to ensure that all their transmissions are in phase or highly correlated in relation to the target area. While easy enough to understand, its implementation is impracticable in the field, because of the need to frequently and precisely change the position and direction of the beam as user equipment or sources of interference move. Moreover, the mechanical method requires the use of antennas with an extremely precise radiation pattern characterised by a narrow main lobe, in order to clearly focus their RF output and enable a quick estimation of each required mechanical movement.

Fortunately, the same beam-forming operation can be implemented electronically, us-

Download PDF of Article ing static antennas. Electronic control of an antenna array's radiation pattern is possible because two or more identical antennas may be configured in such a way that they behave as one single equivalent antenna with a known radiation pattern.

This radiation pattern depends on the type of antenna being used in each element of the array, the position of each element relative to the other elements, and the amplitude and phase of the signal fed to each one. This enables 'smart' antennas to modify their radiation pattern in response to an internal feedback loop while the antenna system is operating. This ability to dynamically alter the direction and shape of an antenna's beam offers great advantages to network operators, improving the efficiency and flexibility of a wireless communication system.

In the continuation of this article, the author expands on the basic design parameters of a smart beam-forming antenna, and shows how – with only a suitable 2-channel signal generator – it is possible to experiment with the fundamentals of beam-forming on the lab bench. Click below for download.

Find Beam-Forming Antenna on EETsearch

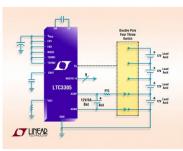

#### DESIGNING ROBUST, FULLY ISOLATED (DATA & POWER) I<sup>2</sup>C/PMBUS DATA INTERFACES

key requirement for indus-Atrial and instrumentation (I&I), telecommunications, and medical applications is a reliable interface for transmitting data. The Inter-Integrated Circuit (I<sup>2</sup>C) bus is a 2-wire bidirectional bus used for low-speed, short-distance communication between integrated circuits. The Power Management Bus (PMBus), a relatively slow 2-wire communications protocol based on I<sup>2</sup>C, is targeted at digital management of power supplies. The PMBus protocol defines an open-standard digital power management protocol that facilitates communication with a power converter or other connected device. Examples of isolated I<sup>2</sup>C applications include:

- Isolated I<sup>2</sup>C, SMBus, or PMBus interfaces

- Level-translating I<sup>2</sup>C interfaces for power supplies

- Networking and Central office switching

- Power-over-Ethernet

- Telecommunication and data

- communication equipment

- Isolated data acquisition systems

- –48 V distributed power systems and modules

#### Dual I2C isolators with DC/DC

The figure compares PMBus isolation using discrete components with a fully integrated solution. The discrete approach requires four optocouplers for isolation, an isolated power supply, and complex analog circuits to prevent latch-up and suppress glitches. The isolated power supply uses a transformer driver IC to drive a discrete transformer, along with a simple rectifier and low-dropout regulator to clean up the isolated rail. This design requires eight ICs and several passive components, and burdens the interface with higher cost, increased PC board area, and lower reliability. The integrated solution (ADM3260) provides a fully isolated bidirectional I2C interface and isolated power with a single IC, plus the

decoupling capacitors and pull-up resistors associated with any I<sup>2</sup>C interface. The ADM3260 is free of glitch and lock-up issues, has UL approved 2.5 kV rms isolation ratings, and is offered in a 20-lead SSOP package. It provides bidirectional isolated data and clock lines and isolated power without the size, cost, and complexity of optocouplers.

This single-chip solution significantly reduces the cost, design time, and PC board area required for an isolated I<sup>2</sup>C interface, while enhancing reliability. It operates from 3.3-V or 5-V supplies without modification, avoiding the design changes that would be necessary with a discrete design, and provides 150 mW of output power at 5 V or 65 mW at 3.3 V, allowing it to power ADCs, DACs, or other

#### **BY MAURICE O'BRIEN**

small systems on the isolated side.

#### Conclusion

Isolated I<sup>2</sup>C/PMBus links in industrial and instrumentation, telecommunications, and medical applications need to be small, robust, and inexpensive. By integrating chip-scale transformer isolation, a single-chip can implement a fully isolated I<sup>2</sup>C/PMBus data link including isolated power. The ADM3260 hot swappable, dual I<sup>2</sup>C isolator with integrated dc-to-dc converter can provide a compact, reliable, low-cost, high-performance solution for these demanding applications while significantly reducing circuit complexity and design time.

**Maurice O'Brien** [maurice.obrien@analog.com] joined Analog Devices in 2002, following his graduation from the University of Limerick, Ireland, with a bachelor's degree in electronic engineering. He currently works as a product marketing manager in the Power Management product line. In his spare time, Maurice enjoys horse riding, outdoor sports, and travel

- Circuit gates pulse train without truncating

- Circuit lets AGC amp hold its gain

- Linear ramp generator uses one op-amp

Circuit lets AGC amp hold its gain

Linear ramp generator uses one op-amp

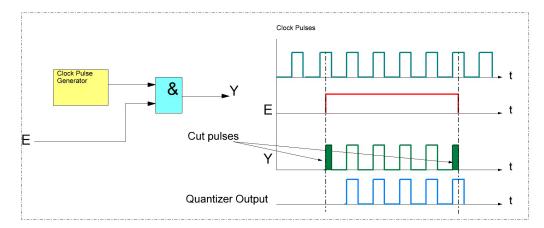

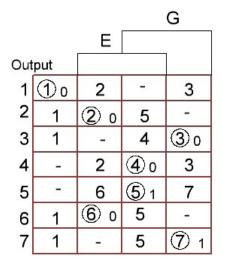

### Circuit gates pulse train without truncating By Viktor Safronov

To gate an integral clock pulse sequence from a continuous source without distorting pulse duration and number is not a trivial task. In most cases, a simple AND gate will cause problems, see Figure 1. Clock pulses pass through the AND gate as long as the asynchronous strobe E is high. If loss or distortion of even one pulse is critical, then the simple AND gate is unsuitable, as the first and the last pulse in the burst will often be distorted (shorter than usual pulse) due to the lack of synchronisation between clock and E.

This Design Idea demonstrates a mathematical approach to synthesise an asynchronous gated circuit able to gate an accurate pulse train from a clock signal without distorting pulse duration. Such circuits are called quantisers (Figure 1).

**Figure 1.** Two ways of gating pulse train, using gate signal *E* and an AND gate (*Y* output), or a quantiser (blue)

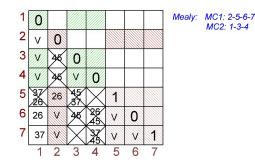

**Figure 2.** Asynchronous finite-state machine (FSM) transition primary table, where 1,2,3,4,5,6,7, the numbers of stable FSM states, are circled (G is the clock input)

**Figure 3.** Final pairs tables by Mealy (left) and Moore (right), where: - MC1: 2-5-6-7 and MC2: 1-3-4 are maximum compatible sets (by Mealy) - MC1: 5-7, MC2: 1-2-6 and MC3: 1-3-4 are maximum compatible sets (by Moore)

Moore:

MC1: 5-7

MC2: 1-2-6

MC3: 1-3-4

## Circuit lets AGC amp hold its gain Linear ramp generator uses one op-amp

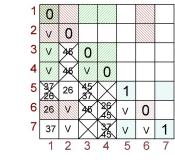

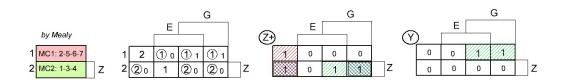

**Figure 4.** Map of Z-coding (by Mealy), compressed state transition table, and Z-Y Karnaugh-Veitch maps

Let's make a state transition table based on the operational principle of a quantiser (Figure 2).

Using Figure 2, let's make final pairs tables according to Mealy and Moore (Figure 3).

As we can see from Figure 3, total coverage by Moore requires a greater number of maximum compliant subsets, i.e., it's worse. On the other hand, the first state is alternatively a part of sets MC2 and MC3, which presents opportunities for extra circuit optimisation. However, we shall not consider this further.

Now, it's easy to draw a compressed state transition table and Karnaugh-Veitch maps for the Z-coding memory element and output gated signal Y (Figure 4).

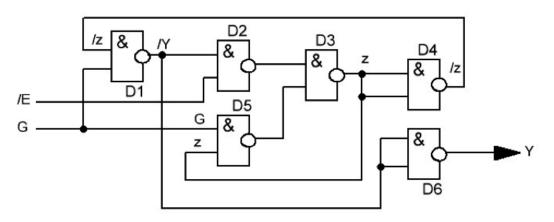

Bearing in mind the Karnaugh-Veitch maps, let's write down logic equations for the synthesized circuit:

$$z^* = \overline{G} \cdot \overline{E} + G \cdot z + \overline{E} \cdot z = \overline{E} \cdot (\overline{G} + z) + G \cdot z = \overline{\overline{E} \cdot \overline{G \cdot z}} \cdot \overline{\overline{G \cdot z}} \quad \& \quad y = G \cdot \overline{z}$$

The minterm [/E  $\cdot$  z] for z+ in this formula is not redundant as it may seem. It plays the important role of a counter-race bridge between minterms [/G  $\cdot$  /E] and [G  $\cdot$  z], eliminating their consecutive races at all edges of G.

- Figure 5. Example implementation of the quantizer, where:

- /E = inverted input of the asynchronous strobe signal

- -G = clock

- Y = quantiser output

It is possible to add some extra features – for example, FLAG. When FLAG is low, the first pulse in the burst is not cut, but incorporated in the burst without affecting its duration. When FLAG is high, the first pulse is cut and excluded from the burst. The state of the FLAG should be kept unchanged until the next strobe pulse, so your equipment has enough time to read it and use for further processing.

This type of quantiser may be useful in designs sensitive not only to the number of pulses in the burst, but to the pulse phase; for example, in radar equipment.

Circuit gates pulse train without truncating

Linear ramp generator uses one op-amp

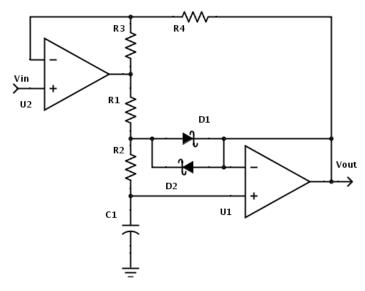

### Circuit lets AGC amp hold its gain By Vladimir Rentyuk

AGC (automatic gain control) amplifiers are frequently-used devices. Their gain is a function of the level of their input signal. The main function of AGC amplifiers is compression of a signal, but sometimes the gain needs to be temporarily frozen. This Design Idea provides just this function.

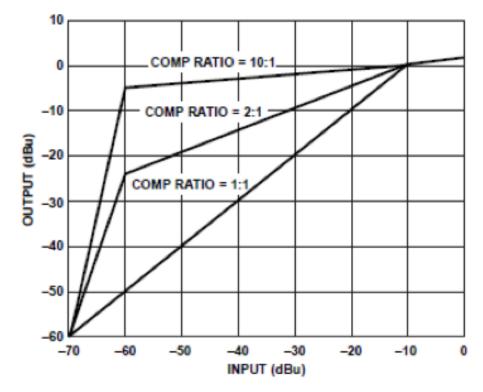

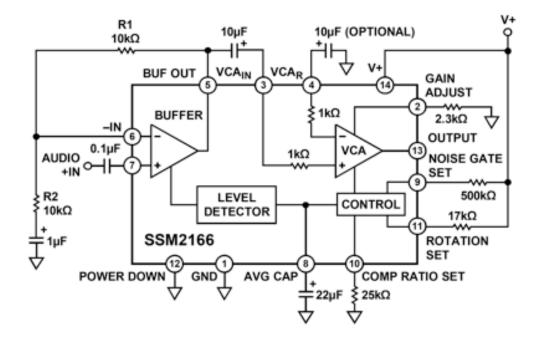

Let's examine this idea with Analog Devices' SSM2166 as an example. The SSM2166 is a microphone preamplifier with variable compression and noise gating whose transfer characteristics are in Figure 1 and typical application diagram in Figure 2.

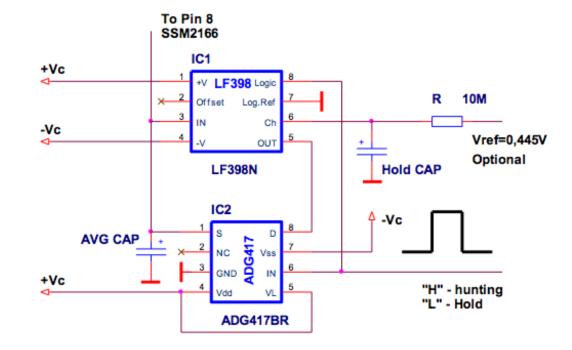

The chip has one interesting feature which isn't presented in the data sheet: we can control the gain using an external voltage applied to pin 8 (AVG CAP). Table 1 shows the observed level detector voltage (pin 8) vs. input voltage. A simple circuit which provides gain-hold capability to the SSM2166 by fixing the output

| Input | Level detector |

|-------|----------------|

| dB    | VDC            |

| 0     | 4,00           |

| -10   | 3,56           |

| -20   | 2,88           |

| -30   | 2,28           |

| -40   | 1,80           |

| -50   | 1,41           |

| -60   | 1,00           |

| -70   | 0,60           |

|       |                |

**Table 1.** Level detector voltage(pin 8) vs. input voltage (observeddependence)

Figure 1. Compression and gating characteristics with 10dB of fixed gain

voltage of the internal level detector is shown in Figure 3. Auto-tracking of the voltage level on the AVG CAP is done by sampleand-hold amplifier IC1 (LF398). This level is duplicated on Hold CAP if IC1.8 is high – the SSM2166 is working in compression mode. When you want to hold the gain, drive this pin low. IC1 will then hold the voltage level on Hold CAP, and analogue switch IC2 (ADG417) will connect IC1's output to pin 8 of the SSM2166, overriding the level detector.

Circuit gates pulse train without truncating

Linear ramp generator uses one op-amp

This Design Idea works with other types of AGC amplifiers, too [Ref.]. But in this case, an analogue switch is unnecessary. In these circuits, a sample-and-hold amplifier should be connected between the level detector and voltage controlled attenuator.

#### Reference

Rentyuk, Vladimir "Use of an AGC Amplifier as a Soft Limiter of Signals", Electronics World, May 2010

#### About the author

Vladimir Rentyuk graduated from Zaporizhzhya Machine Construction Institute (Ukraine) in 1978, earning the equivalent of a master's degree in radio engineering and has worked at the Zaporizhzhya Research Institute of Radio Communication, ZSE Radiopribor, and, since 2002, as a development engineer at Modul-98 Ltd., developer of embedded electronic systems, robotic equipment and image recognition systems. His areas of expertise include analogue design techniques, computer simulations and writing of technical articles that have been published in the US, UK, Russia and Ukraine.

Circuit lets AGC amp hold its gain

#### Linear ramp generator uses one op-amp By Einar Abell

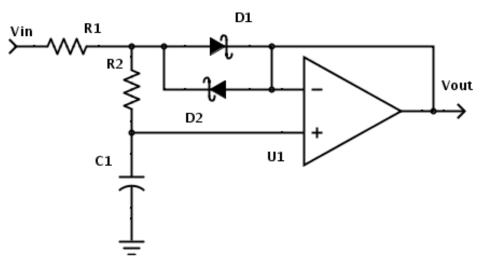

This Design Idea demonstrates a simple way to turn a step input into a ramp of nearly constant slew rate. The basic circuit uses a single op-amp; a circuit built on an integrator will typically require three. Figure 1 shows the basic circuit.

gives best results with fairly large steps, where the slow settling time won't be objectionable.

#### Figure 1. Ramp generator

The op-amp is wired as a voltage follower, with D1 & D2 clamping the input to one diode drop above or below the output. When the input step-changes by a volt or more, the diodes will keep the voltage across R2 at a nearly constant 0.3V (because the output will follow any change on C), creating a constant slew rate at the output of 0.3V/R2C1 V/s. The output will slew to within 0.3V of the input and then follow an RC ((R1+R2)C1) curve until reaching a final value equal to Vin. For best results, R2 should be larger than R1, preferably by factor of ten or more. This simple circuit

#### Figure 2. Improved ramp generator

Figure 2 adds an extra amplifier to make the output slew to within a few millivolts of the input. Amplifier U2 amplifies the difference between the input and the output so as to keep the diode clamp operating until the output voltage nearly reaches the input. The output will slew to within the diode forward voltage divided by the gain of U2 (that is, 1+(R3/R4)). If the gain is made too large, the circuit will become unstable. The slew rate of U2 should be at least ten times (the higher the better) the output slew rate times the gain of U2. U2 needs extra headroom to keep D1 & D2 conducting, which usually means restricting the input so that it is more than one volt away from the max/min output swing of U2.

# SL871 Telit 07BF# De

## productroundup

ROHIM

tronPTI

#### TI grows "nano power" DC/DC module range

Additions to Texas Instruments' Simple Switcher nano modules will, Says TI, "redefine small power supply design" - they are positioned as the smallest-available, high-efficiency 17V and 5V (input) DC/DC power converter blocks that deliver currents in the 100-mA to 2-A range. The 17-V, 0.65-A LMZ21700 and 1-A LMZ21701, as well as the 5-V, 1-A LMZ20501 and 2-A LMZ20502 DC/DC power modules are chip-scale

packages with a surface-mount inductor mounted on top; completing the DC/DC function typically requires only the addition of chip capacitors. The modules, TI says, offer

an overall solution size that is up to 40% smaller than a discrete implementation.

#### **Dimmable lighting-LED chip simplifies driver designs**

Dialog's MR16-lamp dimmable led driver, the iW3662, uses digital control to optimise compatibility with virtually any transformer (electronic or magnetic), to loads as low as 4W; the LED driver is designed to solve transformer and dimmer compatibility issues in low-voltage lighting appli-

cations. The greatest challenge in designing low-voltage MR16 LED retrofit bulbs, Dialog asserts, is the installed base of AC step-down electronic transformers. The iW3662 LED uses digital analytics to detect installed electronic transformers and

dynamically increases the peak loading to latch the transformer.

#### Single coding platform for all STM32 (ARM) MCUs

Designers targeting any of STMicroelectronics' STM32 microcontrollers can now make use of the STMCube software development platform. STM32Cube enables a quick start with any STM32 device and simplifies porting of code from one product series to another. The development platform is available for all devices in volume production, from the ultra-low-power to the very-high-performance series. The platform

#### STM32Cube Supporting all STM32 MCUs

comprises the STM32CubeMX graphical configurator and initialisation C-code generator, which provides wizards that help configure the pin-out, clock-tree,

and peripherals, and meet constraints on power consumption.

#### GaN-on-Si white LEDs deliver more light

Toshiba's latest high-luminous-efficacy white LEDs output luminous flux exceeding 160 lm. This series of high power LEDs is suitable for use in residential, commercial and industrial lighting applications, delivering high luminous flux at room temperature operation. Under conditions

of Ta =  $85^{\circ}$ C, operating current can be driven to 1A and luminous flux is more than 60% greater than that offered by the preceding TL1L3 series. Available in nine colour variations from 2700K to 6500K, the TL1L4 series is built with gallium nitride-

on-silicon (GaN-on-Si) wafer technology in a 3.5 x 3.5 mm lens package.

#### 14-bit, 500 MSPS / 1 GSPS JESD204B, ADC

A D9690 is a 14-bit, 1 Gsample/sec analogue-to-digital converter, designed for sampling wide bandwidth analogue signals of up to 2 GHz. The AD9690 is optimised for wide input bandwidth, high sampling rate, linearity, and low power in a small package. The ADC core features